相关证件:

会员类型:

会员年限:15年

发布时间: 2024/10/18 11:19:31 | 86 次阅读

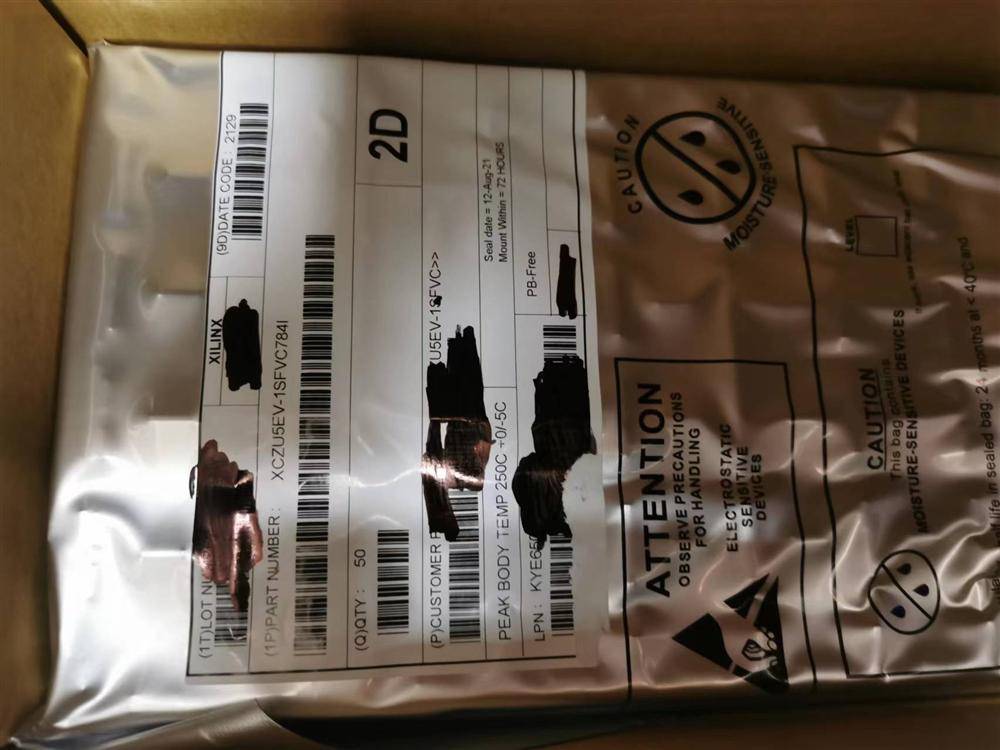

供应,XCZU5EV-1SFVC784I,XILINX/赛灵思,双核Arm

XCZU5EV-1SFVC784I,双核Arm

XCZU5EV-1SFVC784I,双核Arm

XCZU5EV-1SFVC784I,双核Arm

XCZU5EV-1SFVC784I,双核Arm

Zynq?UltraScale%2B? MPSoC系列基于Xilinx?UltraScale? MPSoC架构。这

该系列产品集成了功能丰富的64位四核或双核Arm?Cortex?-A53和

基于Arm Cortex-R5F的双核处理系统(PS)和Xilinx可编程逻辑(PL)UltraScale

单个设备中的架构。还包括片上存储器、多端口外部存储器接口、,

以及丰富的外围连接接口

处理系统(PS)

基于Arm Cortex-A53的应用

处理单元(APU)

四核或双核

CPU频率:高达1.5GHz

可扩展缓存一致性

Armv8-A架构

64位或32位操作模式

托管区安全

64位模式下的A64指令集,

32位模式下的A32/T32指令集

NEON Advanced SIMD媒体处理引擎单/双精度浮点单元(FPU)

CoreSight公司?和嵌入式跟踪宏单元(ETM)

加速器相干端口(ACP)

AXI相干扩展(ACE)

每个处理器核的功率岛选通定时器和中断

Arm通用计时器支持

两个系统级三定时器计数器

一个看门狗计时器

一个全局系统计时器

缓存

32KB级别1,2路集关联

具有奇偶校验的指令缓存(独立于每个CPU)

32KB级别1,4路集关联数据

带ECC的缓存(独立于每个CPU)

1MB 16路集关联二级缓存

带ECC(在CPU之间共享)

基于双核Arm Cortex-R5F

实时处理单元(RPU)CPU频率:高达600MHz

Armv7-R架构

A32/T32指令集

单/双精度浮点单元(FPU)

CoreSight公司? 嵌入微量宏细胞(ETM)

锁定步骤或独立操作

计时器和中断:

一个看门狗计时器

两个三定时器计数器

高速缓存和紧密耦合存储器(TCM)

32KB级别1,4路集关联

带ECC的指令和数据缓存

(独立于每个CPU)

带ECC的128KB TCM(每个独立CPU),可以组合成256KB

在锁步模式下片上存储器

带ECC的PS中的256KB片上RAM(OCM)

高达36Mb的片上RAM(UltraRAM),带ECC输入PL

带ECC的高达35Mb片上RAM(块RAM)

在PL中PL中高达11Mb的片上RAM(分布式RAM)